Mini Display Processor Lite

Features

- Asynchronous timing generation for configurable image resolutions (supporting only landscape)

- Dynamic display screen layering and composition – supporting video and graphics frame blending

- Alpha blending (0 ≤ alpha ≤ 255)

- Alpha blending with hardware cursor (blinking of cursor is also supported)

- Bypass path (bypassing complete dpl pipe)

- Configurable bypass path for displaying video or graphics frame

- Supporting configurable 565 format

- Configurable frame buffer pointers

- Implemented hardware and software way of auto-increment logic to handle multiple frame buffers

- Support for configurable component swapping among ARGB components

Functional Description

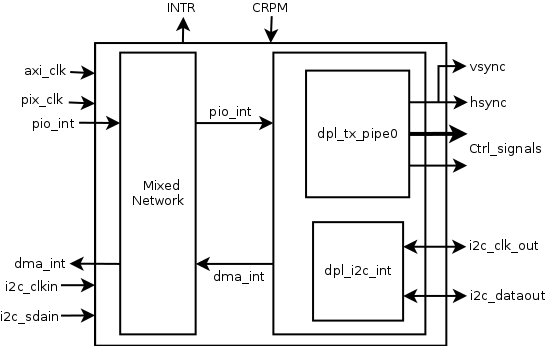

Mini display processor lite (MiniDPL) IP reads video, graphics frame buffer data from DDR through AXI DMA master. The transmitter pipe reads frame buffers for GPB, GPF and Video and blends those (overlaps) according to plane Alpha programmed for each plane and sends through the gamma correction module. This IP outputs pixel data in sync with programmed pixel clock along with timing VSYNC and HSYNC generated from timing generator, as per programmed video standard. In SoC Design, Mini DPL can be interfaced with North Bridge (CPU/Memory) for data transfer and South Bridge (Low-speed Peripherals) for trace/performance interface. It can also be interfaced with external video DAC. The main modules of transmitter pipe are DMA Engine, Alpha Blender, Hardware Cursor, Gamma Corrector, VGA Timing Generator and On screen display controller.

Applications

SoC design for:

- Ultra mobile Computers

- Tablet Computers

- Smart Phones

IP Deliverables

- Synthesizable Verilog RTL

- TTest bench/Test plan

- IP Integration guidelines/Documentation

Download