Viterbi Decoder

System Overview

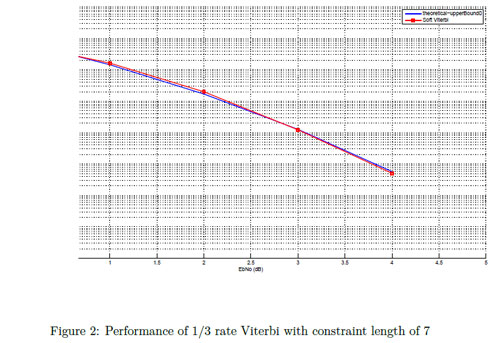

Convolutional FEC codes are very popular because of their powerful error correction capability and are especially suited for correcting random errors. The most effective decoding method for these codes is the soft decision Viterbi algorithm. Depending on the application, the core can be configured for specific code parameters requirements. The highly configurable architecture makes it ideal for a wide range of applications. The Viterbi input data stream is composed of soft bits where it achieves a 2 to 3 dB increase in coding gain over hard-decision decoding.

Features

- Supports 1/N coderates

- Configurable constraint length

- Configurable generator polynomials

- Configurable precision of state metrics

- Soft decision decoding

- Trace-back from the best state

- Automatic normalization

Functional Description

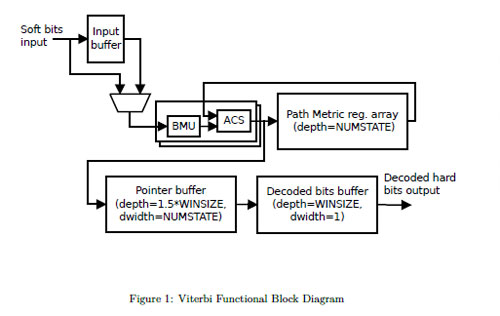

In the Viterbi decoding algorithm, the calculations for the branch and state metrics need to be carried out. A branch metric is the Euclidean distance between the received signal and the output of that branch of the trellis, then the state metric for a certain state is calculated by adding the branch metric for a given transition to the state metric of the previous state on that transition. For the real-time implementation of the algorithm, the state metrics updates along the survivor path can result in overflows in the registers that hold the path metrics since the registers are of finite lengths, so automatic normalization is used to avoid overflow of the state metric registers and also does not add hardware overhead. Then after trace-back from the best state, the decoded bits are then output in the proper order.

Applications

- 3GPP LTE

- IEEE 802.16 WiMax

- DVB

Performance

IP Deliverables

- Synthesizable SystemVerilog

- System Model (C code) and documentation

- Verilog Test Benches

- Documentation

- FPGA testing environment

Download