Reed Solomon

System Overview

- The Reed Solomon Encoder is fed with an input message of K information symbols, the Encoder appends 2T parity symbols to the input message in order to form the encoded codeword.

- The Reed Solomon Decoder receives an (N=K+2T) codeword, and it can locate and correct up to 8 possible symbol errors or up to 14 erasures.

- Both of the Encoder and the Decoder support any input timing pattern, in case of the Encoder; the output timing pattern will be the same as the input. In case of the Decoder; the output timing pattern is fully controlled in order to support any desired pattern by the user.

- The Reed Solomon Decoder keeps track of corrected errors. Input codewords with more than 8 errors are regarded as uncorrectable, and are flagged.

- The Implementation of VK-301 Reed Solomon IP Core targets very low latency, high speed, and low gate count with a simple interface for easy integration on SoC applications.

Features

- High performance Reed Solomon IP Core (Encoder and Decoder)

- Supports error and erasure decoding

- Parameterized codeword length

- Code generator polynomial: (x + λ0)(x + λ1)(x + λ2) . . . (x + λ15)

- Field generator polynomial: x8 + x4 + x3 + x2 + 1

- The core supports any input or output timing pattern

Applications

- Digital Video Broadcasting (DVB)

- Digital Transmission of Television Signals (ITUTJ.83)

- WiMAX (IEEE Std 802.16d)

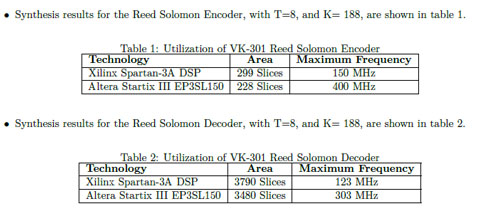

Utilization

IP Deliverables

- Synthesizable Verilog

- System Model (Matlab)

- Verilog Test Benches

- Documentation

The Reed Solomon IP Core is coded in Verilog-2001. No third-party Intellectual properties are contained in this product.

Architecture

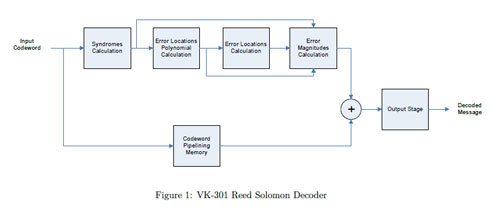

Decoder Architecture

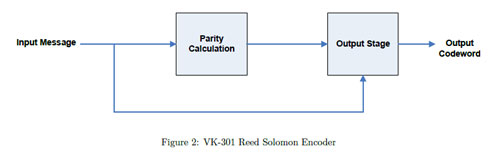

Encoder Architecture

Download